| Product | Details |

|---|---|

MA5100 Series Memory Analyzer MA5100 Series Memory Analyzer |

Memory analyzer supporting DDR5, LPDDR5, LPDDR4 and LPDDR3 performance, margins and capture up to LPDDR5X-8533, LPDDR5-6400, LPDDR4(X)-4267 and LPDDR3-2133 with 1G-Sample acquisition depth, ClockSafe™ and Single Smart Frequency or Sixteen Smart Frequency Analysis. |

MA4100 Series Memory Analyzer MA4100 Series Memory Analyzer |

Memory analyzer supporting DDR4 and DDR3 performance, margins and capture up to DDR4-3200 and DDR3-2133 with 1G-Sample acquisition depth. |

Market drivers in the memory sector have changed. Gone are the days of simply pushing Moore’s Law to ever faster data rates. The memory designs of today and tomorrow must also be smarter than ever before. Today, handheld and wearable computers must draw from a limited battery reserve while serving up fast, responsive, and compelling mobile experiences. Meanwhile the cloud of data centers and server farms that feed us these compelling experiences must continuously grow while simultaneously reducing overhead and environmental impact. These two different markets have the same goals: smarter memory, smarter control systems, and lower power usage.

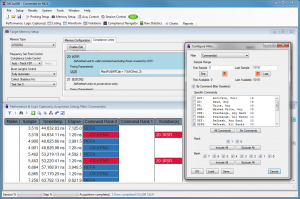

These market demands are driving the development of our MAx100 series memory analyzers. First, smarter memory and smarter control systems require complexity which inevitably introduces more errors. This complexity also introduces more edge cases – some of them fleeting – for errors to hide in. The MAx100 analyzers are designed to handle this complexity with an easy-to-use monitoring system that is always-on and continuously monitoring the memory for errors and to verify proper operation. If a problem exists, the MAx100 will find it and provide the user a wealth of information on the problem’s properties and the bus characteristics that caused the problem.

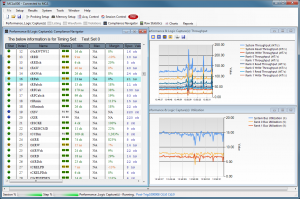

All this new intelligence and complexity exists for a reason. Fundamentally the complexity arises from the memory system’s attempts to continuously respond and optimize performance based on user demands. Here too, the MAx100 has you covered. Designed to capture and provide metrics on performance and optimization, the MAx100 has always-on performance metrics that continuously monitors and reports real-time changes in data rates and clock stalls.

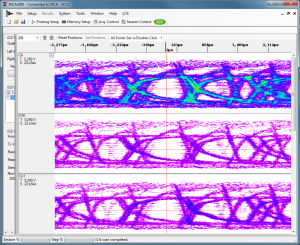

Lastly, some of the raw reductions in power come through decreased voltage swings (as well as other aspects of the memory bus topology) and through user customization of these bus topologies. While the industry continuously designs for higher-speeds, lower voltages, and lower power usage, individual companies take these designs and push them to their limits. Again, the MAx100 excels in this environment by supporting the newest designs the industry has to offer and – even more importantly – provides companies a system that is both easy to set up and is extremely reliable.

The MAx100 supports both the main and mobile memory industry standards of DDR5, DDR4, DDR3, LPDDR5, LPDDR4 and LPDDR3.