# DDRII 400MT/s Vertical Bus Analysis Probe and Software

# **NEX-DDRII400DC**

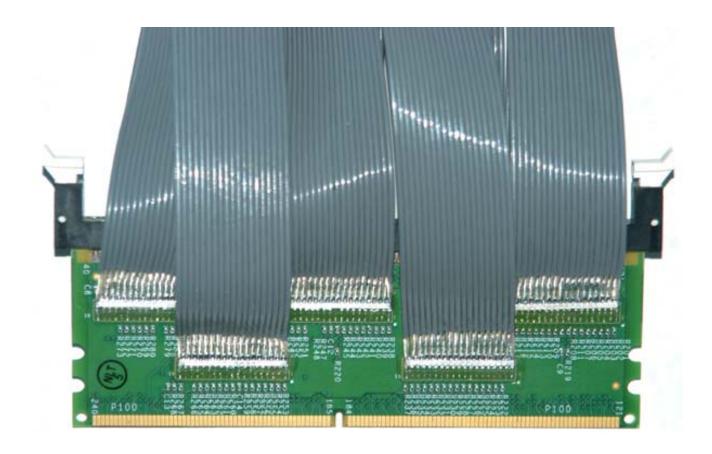

- Very short interposer with Straddle mount DDR2 connector and permanently attached Logic Analyzer probes for use in standard DDR2 DIMM targets that have very limited side-to-side access.

- Acquisition of DDR2-400MT/s Address/Command, Read and Write Data

- Quick and easy connection between the DIMM DDR2 bus and Tektronix Logic Analyzers

- Extender design does not require a dedicated slot

- Impedance controlled, matched trace length design

- No active buffering of the DDR signals

- Accurate 8GHz Timing Analysis

- Simultaneous State and Timing on every channel of the TLA

- Correlation with data acquired from other acquisition modules

## **General Description**

NEX-DDRII400DC allows for the acquisition of Address/Command, Read and Write Data of 240-pin, Unbuffered or Registered DDRII 400 DIMMs.

**Pre-Defined Symbols** for the following Command Cycles allow for easy Trigger Setup:

- Read Col Address Read

- Write Col Address Write

- Mode Register Set

- Row Address Strobe

- Refresh

- Precharge

- Precharge Select Bank

- No Operation

- Ingore Command Data

- Burst Stop

**Selective Clocking** option stores valid cycles and significantly reduces the amount of Idle cycles acquired by the LA. This results in the LA capturing more information of interest and fewer unwanted Idle cycles.

**Oscilloscope Connectivity** to any channel without having to re-probe via the TLA's Enhanced iView Analog Mux capability.

Timing analysis available on all DDRII signals.

**Pre-defined Trigger** setup for the following: Read Col Address Read, Write Col Address Write, Mode Register Set, Row Address Strobe, No Operation, Ignore Command Data, Burst Stop, Refresh, Precharge, and Precharge Select Bank.

The following support package has been included with the NEX-DDRII400DC adapter to support 400MT/s DIMM DDR2:

**SDDR2-2A** software package allows the user to acquire DDRII 400 Read **AND** Write data from a target. This support requires two merged TLA7AA4 or TLA7AB4 136-channel 450MHz state speed acquisition cards. No Logic Analyzer probes are necessary.

## **LA Support / Configuration**

| Acquisition Type | 400 MHz | TLA7xx4 Module Count |

|------------------|---------|----------------------|

| Timing Only      | X       | 2 - merged           |

| Read and Write   | X       | 2 - merged           |

A TLA700 equipped with two 450 MHz state speed acquisition module (TLA7AA4 or TLA7AB4 card) is required for DDR Read and Write Data acquisition. No probes are required.

8 GHz MagniVu Timing and Enhanced iView Analog Mux capabilities are available.

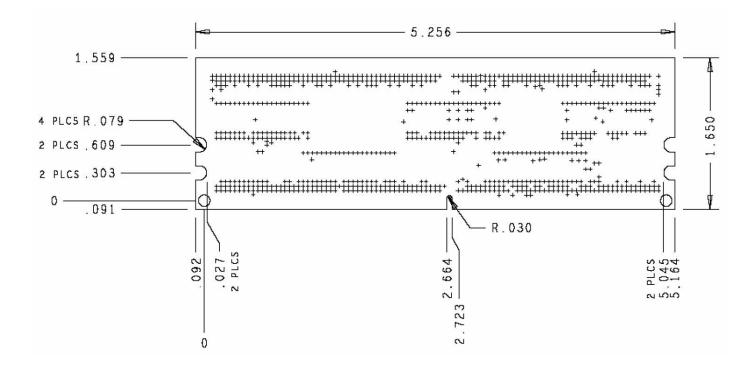

#### **Mechanical Outline**

Approximately 0.37" between DIMM-to-DIMM centers is required for probe clearances. Logic Analyzer connection is provided by probes that are permanently connected to both sides of the adapter.

**NEX- DDRII400DC Mechanical Outline**

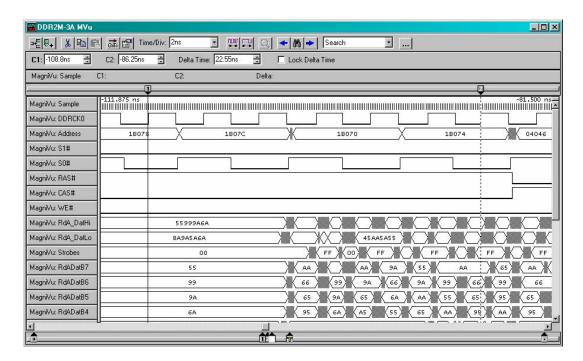

### **Timing Display**

**DIMM DDRII 400 Timing Display**

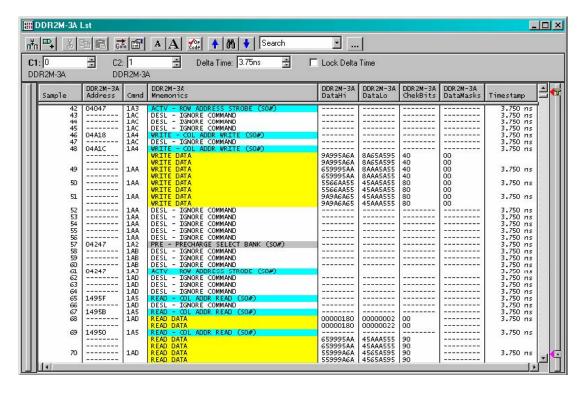

### **State Display**

DIMM DDRII 400 State Display - Software Mode, Address, Data and Command Cycles Only

# **Ordering / Contact Information**

Part Number NEX-DDRII400DC

Includes: NEX-DDRII400DC Adapter

Setup Software

Built in Logic Analyzer probes

Manual

**Postal:** Nexus Technology, Inc.

78 Northeastern Blvd. #2

Nashua, NH 03062

**Telephone:** 877-595-8116

**Fax:** 877-595-8118

**Email:** support@nexustechnology.com

$quotes@nexustechnology.com\\ techsupport@nexustechnology.com$

Website: www.nexustechnology.com

#### Placing an Order

Credit Card orders can be placed directly at 877-595-8116. Purchase orders can be faxed to 877-595-8118.

Nexus Technology, Inc. reserves the right to make changes in design or specification at any time without notice. Nexus Technology, Inc. does not assume responsibility for use of any circuitry described. All trademarks are the property of their respective owners.