Xcelerate™ Series Interposers – New

The Xcelerate™ Series Interposers are designed to meet the rigorous demands of testing high-speed LPDDR5X. Engineered for performance and precision, these interposers support data rates exceeding 10 Gbps. This product family empowers engineers to validate, debug, and optimize next-generation memory systems with unparalleled accuracy and efficiency.

Xcelerate® Series Interposers

All Interposers

The available interposers are listed in the table, ordered by use (oscilloscope or logic analyzer), family (Xcelerate Series, XH Series, etc.), and by BGA package type.

| LPDDR5/5X BGA | JEDEC MO # | Interposers – Oscilloscope | Interposers – Logic Analyzer |

|---|---|---|---|

| 201 | * | * | |

| 245 | MO-363 | * | * |

| 297 | MO-276 | XH Series | * |

| 305 | MO-276 | * | * |

| 315 | MO-338A | Xcelerate™ Series – New 14.4G Interposer | XH Series Direct Attach |

| XH Series | |||

| XH Series (EdgeProbe™) | |||

| 436 | MO-317 | * | * |

| 441 | MO-342 | XH Series | * |

| 496 | MO-344 | XH Series | XH Series |

| 561 | MO-352 | * | * |

| 563 | MO-350B | * | * |

| Custom | Any | * | * |

* If you don’t see what you need, please contact us for the most up to date information.

Summary of LPDDR5 and LPDDR5X

LPDDR5 (Low Power Double Data Rate 5) is a high-performance, low-power memory standard designed primarily for mobile devices such as smartphones, tablets, and ultrathin laptops. Introduced by JEDEC in 2019, it offers significant improvements over its predecessor, LPDDR4, including higher data rates (up to 6400 MT/s), improved power efficiency, and enhanced bandwidth. LPDDR5 achieves this through features like a 16n prefetch architecture, dynamic voltage scaling, and advanced power-saving modes such as deep sleep and self-refresh. It operates at a lower voltage (typically 0.6V for the I/O and 1.05V for the core) and supports a bank group architecture to optimize data access, making it ideal for energy-constrained, high-performance applications.

LPDDR5X is an enhanced version of LPDDR5, introduced later to push performance boundaries further. It offers higher data rates (exceeding 9,600 MT/s with interposer support up to 14,400 MT/s), improved signal integrity, and greater power efficiency compared to standard LPDDR5. LPDDR5X achieves these gains through optimizations like better equalization techniques, enhanced clocking mechanisms, and tighter timing parameters. While maintaining compatibility with LPDDR5’s low-power ethos, LPDDR5X targets more demanding applications, such as flagship mobile devices, AI accelerators, and automotive systems, where maximum bandwidth and efficiency are critical. Both LPDDR5 and LPDDR5X are pivotal in enabling modern computing demands, balancing speed and power efficiency for next-generation devices.

Interposers for Interfacing Test Equipment to the LPDDR5 Bus

Testing and validating LPDDR5 and LPDDR5X memory systems require specialized tools due to their high-speed operation and complex signaling. Interposers are critical hardware components designed to bridge the gap between test equipment (such as logic analyzers, oscilloscopes, or protocol analyzers) and the LPDDR5 memory bus. These interposers physically connect to the memory bus on a target device, providing a non-intrusive way to monitor, capture, and analyze signals without disrupting normal operation.

Nexus Technology’s LPDDR5(X) interposers are engineered to handle the standard’s high data rates (up to 14.4 GT/s for LPDDR5X), low-voltage signaling, and multi-channel architecture. These interposers enable engineers to perform tasks like compliance testing, debugging memory-related issues, and verifying performance metrics (e.g., latency, bandwidth, and power consumption). As LPDDR5 and LPDDR5X adoption grows, interposers remain essential for ensuring reliability and performance in cutting-edge applications.

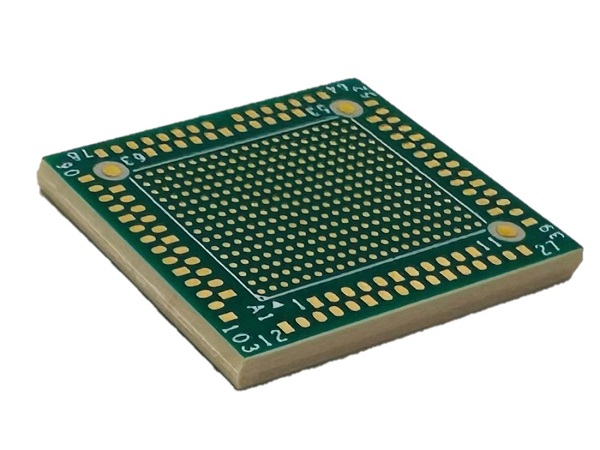

Interposer Packages

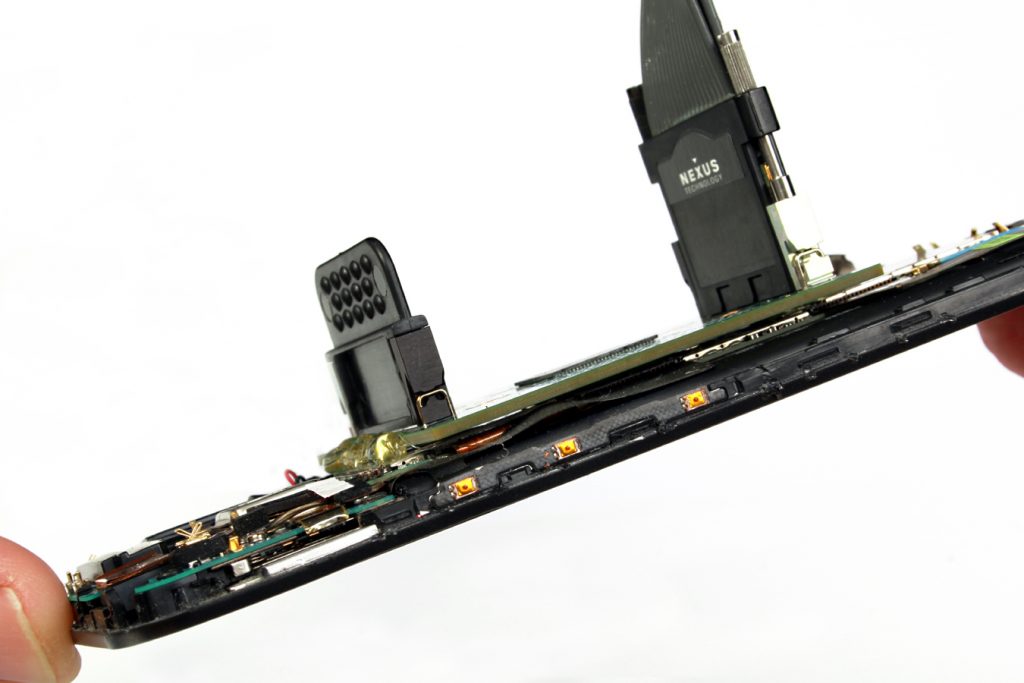

Nexus Technology’s LPDDR5(X) interposers, available in standard and non-standard BGA packages, are installed directly to the target board.

Attachment Service

Nexus Technology’s expert attachment service provides a ready-to-go test solution customized to your application. We will attach the interposer and any additional accessories to your application’s target. We can also power-on and test your application to confirm functionality.

Oscilloscope / Electrical Analysis Interposers

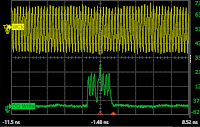

Nexus Technology’s oscilloscope interposers are designed to facilitate the testing and analysis of memory buses using an oscilloscope. These interposers act as a physical and electrical interface between the high-speed LPDDR5(X) memory system on a target device (e.g., a smartphone or embedded system) and the oscilloscope, enabling engineers to capture and analyze analog signals such as voltage waveforms, timing characteristics, and signal integrity at data rates exceeding 10 GT/s.

LPDDR5 interposers are engineered for:

- Signal Integrity Analysis: Enable precise measurement of signal quality (e.g., eye diagrams, jitter, noise) to ensure the memory bus meets JEDEC specifications.

- Timing Verification: They help validate critical timing parameters like setup/hold times, clock skew, and data alignment.

- Debugging: Assist in diagnosing issues like crosstalk, reflections, or power supply noise affecting LPDDR5 performance.

Compliance Testing: Enable engineers to verify that LPDDR5 implementations adhere to industry standards.

Logic Analyzer / Protocol Compliance Analysis Interposers

Logic analyzer LPDDR5 interposers are specialized hardware tools designed to interface LPDDR5(X) memory buses with a logic analyzer, enabling the capture and analysis of digital signals and protocol-level behavior. These interposers connect the high-speed LPDDR5(X) memory system on a target device (e.g., a mobile device or embedded system) to a logic analyzer, allowing engineers to monitor and decode digital transactions at data rates up to 9600 MT/s.

LPDDR5 interposers for logic analyzers are engineered for:

- Protocol Analysis: They capture and decode LPDDR5 bus transactions (e.g., commands, addresses, and data transfers) to verify correct operation and adherence to JEDEC standards.

- Timing Validation: They measure digital timing relationships, such as clock-to-data alignment or command sequencing, at a logic level.

- Debugging: They help identify issues like protocol violations, state machine errors, or data corruption in the memory system.

Performance Monitoring: They enable tracking of bus utilization, latency, and throughput for optimization purposes.

Product List

- LPDDR5 297 Ball XH Series Direct Attach Interposer

- LPDDR5 315 Ball Compliance Interposer

- LPDDR5 315 Ball XH Series Direct Attach Interposer

- LPDDR5 315 Ball XH Series EdgeProbe Interposers

- LPDDR5 441-Ball Direct Attach Interposer

- LPDDR5 496 Ball Compliance Interposer

- LPDDR5 496 Ball XH Series Direct Attach Interposer

- LPDDR5X-14400 Xcelerate™ Series 315-Ball BGA Interposer | Oscilloscope